# EE4390 Microprocessors

Lesson 1

Course Overview,

68HC12 Overview

#### Overview

- Course overview

- Course policies

- Computers and Embedded Controllers

- 68HC12 Overview

# Computers and Embedded Controllers

- All computers contain four hardware modules

- central processing unit (CPU)

- memory

- input/output devices

- buses

- Reference Figure 1.1, pg 5

# Central Processing Unit

- Governs order of instruction execution

- Controls access to memory and I/O devices

- Performs arithmetic and logical operations

- Handles interrupt services

- Contains: ALU, control unit, internal registers, timers, buses

- Speed based on clock speed

#### Memory

- Contains instructions and data

- von Neumann architecture -- instructions and data stored in the same memory

- Memory technologies:

- RAM

- ROM

#### I/O Devices

• Input/Output devices:

#### Buses

- Pathways connecting computer components

- address: specify address locations where data and instructions reside in memory

- data: carries instructions and data to and from memory

- control: sends and receives control commands among system components

## Terminology

- Microprocessor: CPU units packaged in a single chip

- Microcomputer: computer that uses the microprocessor as its CPU (e.g. PC)

- Microcontrollers (a.k.a. embedded controllers): all computer components in a single VLSI (Very Large Scale Integration) chip

## **Applications**

• How many embedded controllers have you used today?

#### 68HC12 Overview

- Introduced by Motorola 1997

- Instruction Set

- 209 instructions

- multiple addressing modes (where's the data!)

- CPU12

- 16 bit processor

- variants:

- "A4": expanded mode, 8 MHz

- "B32": single chip mode, 8 MHz

- HCS12 series: larger onboard memory, 25 MHz

- Clock speed: 16 MHz crystal, divide by 2 for 8 MHz system clock

- clock generated by crystal or ceramic resonator

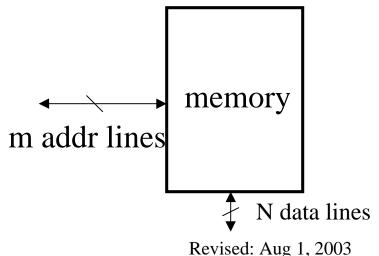

# Memory Concepts - Review

- Width: M bits, number of data lines, determines size of operand

- Length: number of separately addressable locations,  $2^{\text{#addr lines}} = \text{#memory locations}$

### Memory Concepts - Review

- RAM

- read/write

- volatile

- faster access time

- variants

- SRAM

- DRAM

- applications

- variables

- dynamic memory allocation

- heaps, stacks Revised: Aug 1, 2003

- ROM

- read only

- non-volatile

- slower

- variants

- ROM, PROM, EPROM, EEPROM (byte-addressable, FLASH)

- applications

- programs

- constants, codes, etc.

# Memory Concepts - Review

$$2^{10} = 1024$$

$2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10} 2^{10$

#### Other common conversions:

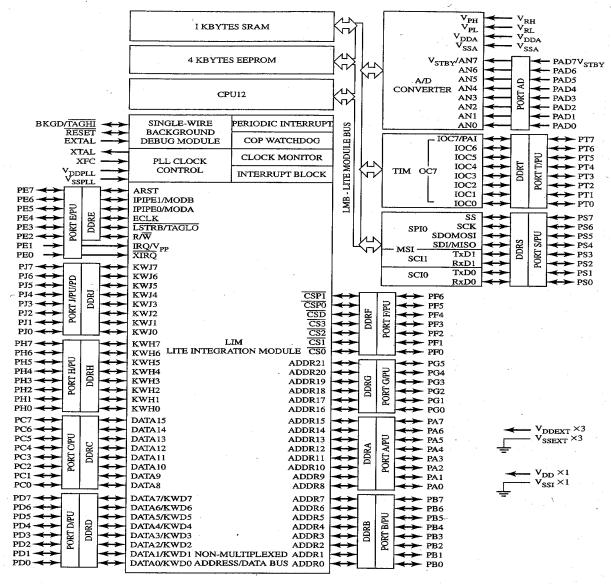

#### 68HC12 Overview (cont)

- Memory: 1K-byte RAM, 4K-bytes EEPROM, expandable to 5M-bytes

- Serial communications: SCI and SPI

- asynchronous vs. synchronous communication

- SCI: communications asynchronous

- SPI: extend features of 68HC12 synchronous

- 8 channel analog-to-digital converter

- 8 channel timer

- input capture, output compare, pulse accumulation

- Background Debug Mode (BDM) troubleshooting

- Memory-mapped input/output

Figure 1.3 The block diagram of the MC68HC812A4 (Motorola).

"Copyright of Motorola, Used by Permission" Revised: Aug 1, 2003

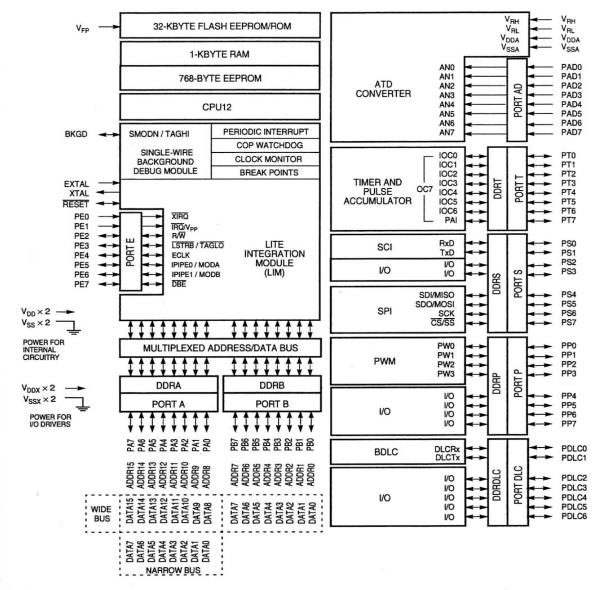

#### 1.6 Block Diagrams

Figure 1-1. Block Diagram for MC68HC912B32 and MC68HC12BE32

Revised: Aug 1, 2003