### EE4800-03 Embedded Systems Design

Lessons 7-10 - Exceptions -Resets and Interrupts

- Polling vs. Interrupts

- Exceptions: Resets and Interrupts

- 68HC12 Exceptions

- Resets

- Interrupts: Maskable and Non-maskable

- 68HC12 Interrupt Response

- Exception Vector

- Exception Priority

- Programming an Interrupt Service Routine

- Polling versus interrupts

- polling: constantly monitoring for flag to set

- program is tied up waiting for flag

- inefficient use of processor

- interrupt: processor tells program when event has occurred

- program can be executing other tasks

- efficient use of processor

- EX] sequentially ask question vs you ask me

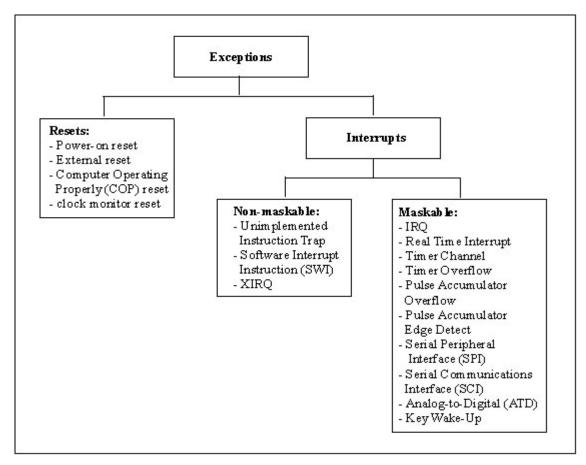

- Resets: returns 68HC12 to known, well-defined state after detected fault

- power-on reset

- Computer Operating Properly (COP) reset

- Clock Monitor reset

- External reset

- Interrupts planned, but unscheduled high priority event

- non-maskable: may not be turned off by user

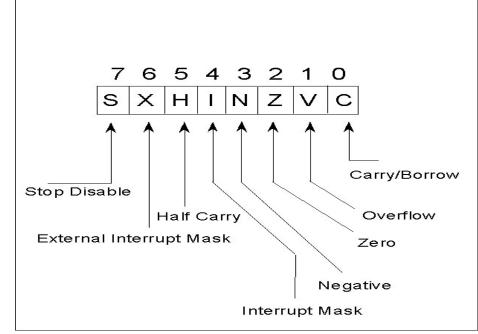

- maskable: turned on and off by user with "I" bit in CCR

- "I" bit controlled with CLI and SEI command

- CLI: Clear Interrupt Mask turns interrupt system on

- SEI: Set Interrupt Mask turns interrupt system off

- Need to turn on specific interrupt locally

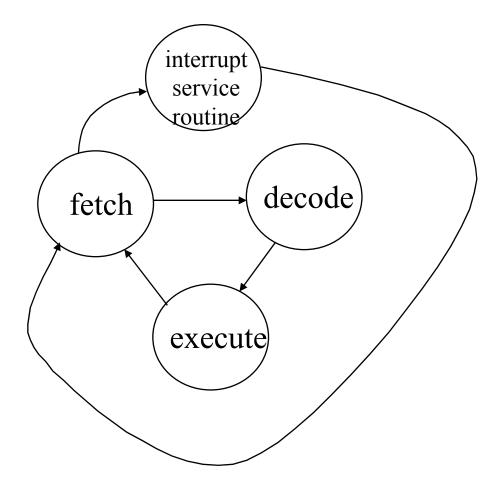

#### **68HC12 Interrupt Response**

#### **68HC12 Interrupt Response**

- Interrupt Vector

- location of ISR

- located in upper 128 bytes of memory

- user must tie Vector to ISR

- Interrupt Priority

- determines order of

execution when multiple

interrupts occur

- Interrupt Service Routine (ISR) - user written response routine to interrupt event

#### **68HC12 Interrupt Response**

#### - Interrunt Priority -

|              | Vector Address        | Interrupt Source               | CCR   | Local Enable                | <b>HPRIO</b> Value to |

|--------------|-----------------------|--------------------------------|-------|-----------------------------|-----------------------|

|              | · · ·                 |                                | Mask  |                             | Elevate               |

|              | <b>\$FFFE, \$FFFF</b> | Reset                          | none  | none                        | <b>_</b> ·            |

|              | \$FFFC, \$FFFD        | COP Clock Monitor Fail Reset   | none  | CME, FCME                   | _                     |

| Non-maskable | \$FFFA, \$FFFB        | COP Fail Reset                 | none  | cop rate selected           | -                     |

|              | \$FFF8, \$FFF9        | Unimplemented Instruction Trap | none  | none                        | -                     |

|              | \$FFF6, \$FFF7        | SWI                            | none  | none                        | -                     |

|              | \$FFF4, \$FFF5        | XIRQ                           | x bit | none                        | -                     |

| Maskable     | \$FFF2, \$FFF3        | IRQ or Key Wake Up D           | 1 bit | IRQEN, KWIED[7:0]           | \$F2                  |

|              | \$FFF0, \$FFF1        | Real Time Interrupt            | 1 bit | RTIE                        | \$F0                  |

|              | \$FFEE, \$FFEF        | Timer Channel 0                | 1 bit | TC0                         | \$EE                  |

|              | \$FFEC, \$FFED        | Timer Channel 1                | 1 bit | TC1                         | \$EC                  |

|              | \$FFEA, \$FFEB        | Timer Channel 2                | 1 bit | TC2                         | \$EA                  |

|              | \$FFE8, \$FFE9        | Timer Channel 3                | 1 bit | TC3                         | \$E8                  |

|              | \$FFE6, \$FFE7        | Timer Channel 4                | 1 bit | TC4                         | \$E6                  |

|              | \$FFE4, \$FFE5        | Timer Channel 5                | 1 bit | TC5                         | \$E4                  |

|              | \$FFE2, \$FFE3        | Timer Channel 6                | 1 bit | TC6                         | \$E2                  |

|              | \$FFE0, \$FFE1        | Timer Channel 7                | 1 bit | TC7                         | \$E0                  |

|              | \$FFDE, \$FFDF        | Timer Overflow                 | 1 bit | TOI                         | \$DE                  |

|              | \$FFDC, \$FFDD        | Pulse Accumulator Overflow     | 1 bit | PAOVI                       | \$DC                  |

|              | \$FFDA, \$FFDB        | Pulse Accumulator Input Edge   | 1 bit | PAII                        | \$DA                  |

|              | \$FFD8, \$FFD9        | SPI Serial Transfer Complete   | 1 bit | SPIOE                       | \$D8                  |

|              | \$FFD6, \$FFD7        | SCI 0                          | 1 bit | TIE0, TCIE0,<br>RIE0, ILIE0 | \$D6                  |

|              | \$FFD4, \$FFD5        | SCI 1                          | 1 bit | TIE1, TCIE1,<br>RIE1, ILIE1 | \$D4                  |

|              | \$FFD2, \$FFD3        | ATD                            | 1 bit | ADIE                        | \$D2                  |

|              | \$FFD0, \$FFD1        | Key Wakeup J (stop wakeup)     | 1 bit | KWIEJ[7:0]                  | \$ <b>D</b> 0         |

|              | \$FFCE, \$FFCF        | Key Wakeup H (stop wakeup)     | 1 bit | KWIEH[7:0]                  | \$CE                  |

|              | \$FF80-\$FFCD         | Reserved                       | 1 bit |                             | \$B0-\$CC             |

Highest Priority

> Lowest Priority

"Copyright of Motorola, Used by Permission"

Revised: Dec 15, 2003

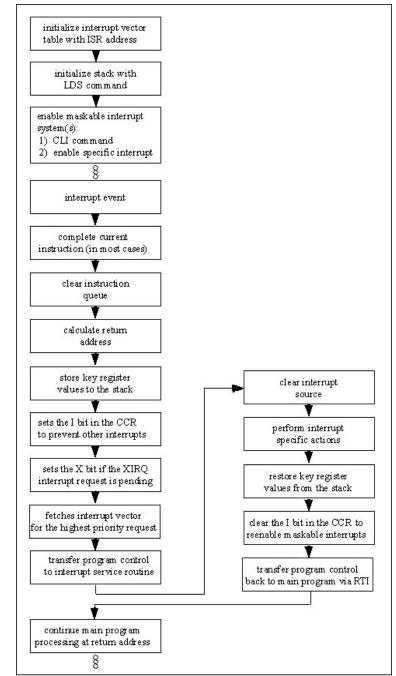

#### Programming an Interrupt Service Routine

- Determine how interrupt is enabled

- global: CLI

- local enable bit

- Initialize Vector Table

- directive approach

- EVB SetUserVector

- Initialize Stack

- Enable interrupt

- Write the specific ISR

Initialize the microprocessor for the interrupt.

- Initialize the stack this is done through compiler settings

- Initialize any other necessary systems on the HC12.

- Initialize the interrupt vector table. You will need to use a special header file and code.

- Header file is on your computer and is called **abbie.h** (change name).

- Code to set up your function to be an interrupt service routine will be similar to the following:

This part declares your function as an interrupt service routine. #pragma interrupt\_handler toggle\_isr

• This part fills the appropriate vector with the address of your interrupt service routine.

#pragma abs\_address: 0x0B2A

void (\*Timer\_Channel\_2\_interrupt\_vector[])()={toggle\_isr};

#pragma end\_abs\_address

- Make sure the interrupt you will be using is cleared to start.

- Initialize local interrupts.

- Initialize the interrupt system using the CLI command (With this header file use CLI(); ). Do this step last so that you aren't inadvertently setting off interrupts before you finish initializing the system.

- Write the interrupt service routine to handle the interrupt.

# Programming an ISR - an example

Table 1. RAM Interrupt Vectors **Interrupt Name RAM Vector Location** BDLC (Key Wakeup J) \$0B10, \$0B11 ATD \$0B12, \$0B13 SCI \$0B16, \$0B17 SPI \$0B18, \$0B19 Pulse Accumulator Input Edge \$0B1A, \$0B1B Pulse Accumulator Overflow \$0B1C, \$0B1D Timer Overflow \$0B1E, \$0B1F **Timer Channel 7** \$0B20, \$0B21 Timer Channel 6 \$0B22, \$0B23 **Timer Channel 5** \$0B24, \$0B25 **Timer Channel 4** \$0B26, \$0B27 Timer Channel 3 \$0B28, \$0B29 Timer Channel 2 \$0B2A, \$0B2B Timer Channel 1 \$0B2C, \$0B2D Timer Channel 0 \$0B2E, \$0B2F **Real Time Interrupt** \$0B30, \$0B31 IRQ \$0B32, \$0B33 XIRQ \$0B34, \$0B35 SWI \$0B36, \$0B37 Unimplemented Instruction Trap \$0B38, \$0B39 COP Failure \$0B3A, \$0B3B **COP Clock Monitor Fail Reset** \$0B3C, \$0B3D \$0BEF, \$0BFF Reset

Revised: Dec 15, 2003

Example] In this task you will need to simultaneously generate two square waves with different frequencies. For one wave use the month and day of your birthday and for the second use the month and day of your Lab TA's birthday. Verify that the waves are being generated simultaneously and that they have different frequencies with the oscilloscope.

```

#include <abbie.h>

void toggle1_isr(void); //function prototype

void toggle2_isr(void);

#pragma interrupt_handler toggle1_isr //define as interrupt

#pragma interrupt handler toggle2 isr

```

```

#pragma abs_address: 0x0B28

void (*Timer_Channel_3_interrupt_vector[])()={toggle2_isr};

void (*Timer_Channel_2_interrupt_vector[])()={toggle1_isr};

#pragma end_abs_address

```

```

// Define function initialize

void initialize(void);

void main(void) {

initialize();

// Initialize the timer system

TMSK1 = 0 \times 0C;

TFLG1 = 0xFF;

CLI();

// Initialize interrupts

// Continuous loop

while(1)

// Wait for interrupts

{

;

}

```

/\* Function: initialize: enables the timer and sets up the M-Clk \*/

```

void toggle1_isr(void) {

TFLG1 = 0x04;

TC2 += 9091;

}

void toggle2_isr(void)

{

TFLG1 = 0x08;

TC3 += 4854;

}

```

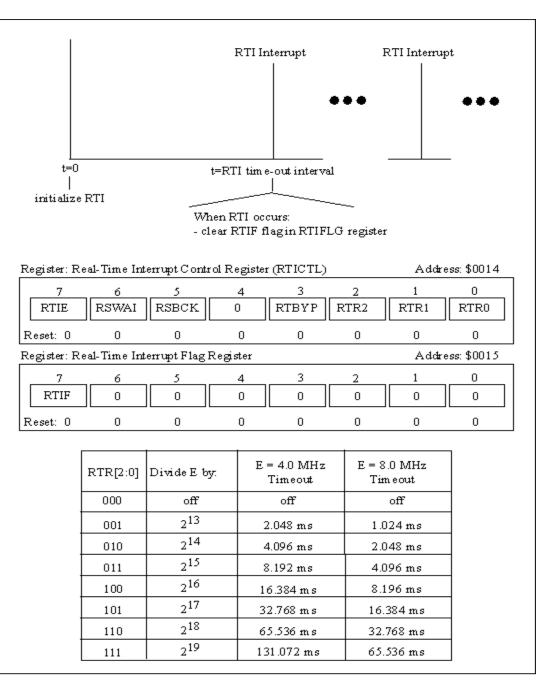

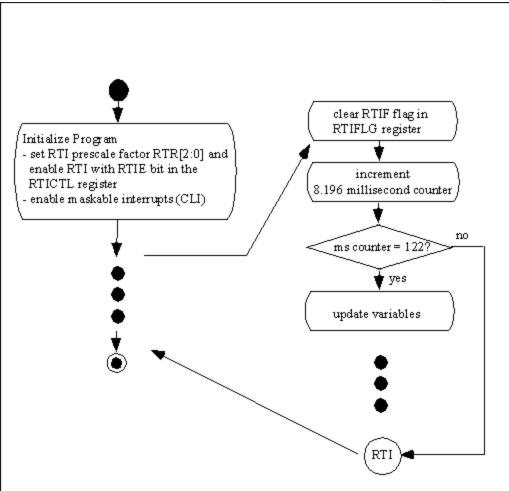

- Reminds processor to perform required actions on a regular basis.

- Two key registers:

- RTI Control Register (RTICTL): used to enable RTI and set interrupt rate

- RTIE: (1) to enable

- RTR[2:0] to set interrupt rate

- RTI Flag Register (RTIFLG): bit 7 RTIF

- Reset by writing "1" to RTIF

```

/*-----*/

/*MAIN PROGRAM: This program keeps track of clock time using the Real Time

*/

/*Interrupt. The RTI generates an interrupt every 8.192 ms. The RTI isr

*/

*/

/*keeps track of elapsed time.

/*-----*/

/*include files*/

#include<912b32.h>

/*function prototypes*/

void RTI isr(void);

/*Real Time Interrupt - ISR*/

/* interrupt pragma */

#pragma interrupt handler RTI isr

/*initialize vector table*/

#pragma abs address: 0xF7F0

void (*RTI interrupt vector[])()={RTI isr};

#pragma end abs address

```

```

/*global variables*/

unsigned int ms ctr, sec ctr, mins ctr, hrs ctr, days ctr;

```

```

void main(void) {

/*initialize timer variables*/

ms ctr = 0;

sec ctr = 0;

mins ctr = 0;

hrs ctr = 0;

days ctr = 0;

RTICTL = 0 \times 84;

/*Enable RTI int, 8.196ms RTI*/

CLI();

/*Initialize interrupts*/

while(1)

{

/*wait for interrupt*/

}

_____*/

-----*/

```

23

\*/

```

/*-----*/

/*Function: RTI isr: RTI interrupt occurs every 8.196 ms

*/

/*-----*/

void RTI isr(void) {

RTIFLG = 0 \times 80;

/*reset RTI Interrupt Flag*/

/*update milliseconds*/

/*increment ms counter */

ms ctr = ms ctr+1;

/*update seconds*/

if(ms ctr == 122)

/*counter equates to 1000 ms at 122*/

{

ms ctr = 0;

/*reset millisecond counter*/

/*increment seconds counter*/

sec ctr = sec ctr +1;

}

```

```

/*update minutes*/

if(sec ctr == 60)

sec ctr = 0;

/*reset seconds counter*/

mins ctr = mins ctr + 1;

/*increment minutes counter*/

/*update hours*/

if (mins ctr == 60)

{

/*reset minutes counter*/

mins ctr = 0;

hrs ctr = hrs ctr + 1;

/*increment hours counter*/

/*update days*/

if (hrs ctr == 24)

/*reset hours counter*/

hrs ctr = 0;

days ctr = days ctr +1;

/*increment days counter*/

Revised: Dec 15, 2003

```

## Multiple Interrupts

- Allows multiple events to occur "simultaneously"

- Interrupt Priority

- HC12 shuts off interrupt system during ISR

- May want to manually re-enable to allow system to respond to higher priority events

- Must carefully study interaction of interrupts

- Very difficult to troubleshoot malfunctioning system